# OPTOIO-PCIe16 ULTRA

EDP-No.: A-829410

16 optocoupler isolated digital inputs

16 optocoupler isolated digital outputs

16\*32 -bit Counter

Timer

OC and IC Units

Board Identification

#### Copyright<sup>©</sup> 2017 by Messcomp Datentechnik GmbH

This documentation is copyright by Messcomp Datentechnik GmbH. All rights are reserved.

Messcomp Datentechnik GmbH reserves the right to modify the products described in this manual at any time and without preannouncement.

No parts of this manual are allowed to be reproduced, copied, translated or transmitted in any way without a prior written consent of Messcomp Datentechnik GmbH.

#### **Registered Trademarks**

Windows®, Visual Basic®, Visual C++®, Visual C#® are registered trademarks of Microsoft.

wasco® is registered trademark.

Linux® is registered trademark.

Ubuntu® is registered trademark.

LabVIEW® is registered trademark

Other product and company names mentioned may be trademarks of their respective owners.

#### Disclaimer

The company Messcomp Datentechnik GmbH assumes no liability for the use of the interface card OPTOIO-PCle16<sub>ULTRA</sub> and this documentation, neither for direct nor indirect damages..

# **Table of Contents**

| 1. | Description                                                  | 5  |

|----|--------------------------------------------------------------|----|

| 2. | Installation of the OPTOIO-PCIe16ultra                       | 6  |

|    | 2.1 Installation of the card into your system                | 6  |

| 3. | Connectors                                                   | 7  |

|    | 3.1 Position of the connector plugs on the board             |    |

|    | 3.2 Pin assignment of CN1                                    |    |

|    | 3.4 Pin assignment from CN2 to D-Sub37 (plug relocation kit) |    |

| 4. | System Components                                            | 11 |

| •  | 4.1 Block Diagram                                            |    |

|    | 4.2 Access to the system components                          |    |

|    |                                                              |    |

| 5. | 16 Optocoupler Isolated Digital Inputs                       | 13 |

|    | 5.1 Pin assignment of the input optocouplers                 |    |

|    | 5.2 Input voltage ranges                                     |    |

|    | 5.3 Input wiring                                             |    |

|    | 5.4 Input current                                            | 10 |

|    | 5.6 Optocoupler inputs with digital filters                  |    |

|    | 5.7 Interrupt functions of the optocoupler inputs            |    |

|    | 5.8 Port Addresses                                           |    |

| 6. | 16 Optocoupler Outputs                                       | 25 |

|    | 6.1 Pin assignment of the output optocouplers                | 25 |

|    | 6.2 Optocoupler data                                         |    |

|    | 6.3 Output wiring                                            | 25 |

|    | 6.4 Functions of the optocoupler outputs                     |    |

|    | 0.0 FUIT Addresses                                           |    |

| 7. | Counter                                                      | 30 |

|    | 7.1 Basic function                                           |    |

|    | 7.2 Interrupt function                                       |    |

|    | 7.3 Port Addresses                                           | 31 |

| 8. | Timer                                                        | 37 |

| -  | 8.1 Using as an interval interrupt trigger                   |    |

|    | 8.2 Port Addresses                                           |    |

|    |                                                              |    |

| 9. I | Input Capture Unit                                    | 41 |

|------|-------------------------------------------------------|----|

|      | 9.1 Continuous measurement of periodic signals        | 41 |

|      | 9.2 Port Addresses                                    | 43 |

| 40   | Output Output Half                                    | 47 |

| 10.  | Output Compare Unit                                   |    |

|      | 10.1 PWM                                              |    |

|      | 10.2 Pulse output                                     | 49 |

| 11.  | Interruptcontroller                                   | 55 |

|      | 11.1 Port Addresses                                   | 57 |

| 12.  | Board Identification                                  | 69 |

|      | 12.1 Port Addresses                                   |    |

| 13   | Programming under Windows®                            | 71 |

| 10.  | 13.1 Installation of the Windows® driver              | 71 |

|      | 13.2 Installation of the Windows® development files   |    |

|      | 13.3 Programming the OPTOIO-PCIe16 with wasco® driver |    |

|      | 13.4 Access to the OPTOIO-PCIe16 <sub>ULTRA</sub>     |    |

|      | 13.5 Assignment of the Memory Mapped I/O Addresses    |    |

| 14.  | Linux® Programming                                    | 76 |

|      | 14.1 Installing the Linux® driver                     |    |

|      | 14.2 Supported Linux Distributions/Kernel versions    |    |

|      | 14.3 Programming the OPTOIO-PCIe16 with wasco® driver | 76 |

|      | 14.4 Access to the OPTOIO-PCIe16ultra                 | 77 |

|      | 14.5 Assignment of the Memory Mapped I/O addresses    | 77 |

| 15.  | Accessories                                           | 78 |

|      | 15.1 Compatible wasco® accessories                    |    |

|      | 15.2 Connection Technique (application examples)      | 78 |

|      | 15.3 Single components for self-assembly              | 79 |

| 16.  | Troubleshooting                                       | 80 |

| 17.  | Specifications                                        | 81 |

| 12   | Product Liability Act                                 | QΩ |

|      | •                                                     |    |

| 19.  | Declaration of Conformity                             | 84 |

# 1. Description

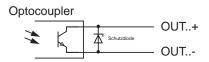

OPTOIO-PCIe16ULTRA (board name: WASCO-PCIe8117) provides 16 digital inputs and 16 digital outputs, every single channel is galvanically isolated by optocouplers of high quality. Special high-power output optocouplers manage a switching current of up to 150 mA. Each input or output is protected from harmful voltage peaks and pulses by additional protection diodes. You easily can adjust two different input voltage ranges by setting jumpers. A programmable filter can be assigned to each input channel to hide input pulses below an adjustable impulse duration.

In addition to the galvanically isolated inputs and outputs several counters are available as well as Output Compare units (e.g. PWM) and Input Capture units (e.g. for period measurement). All optocoupler inputs, counters, IC units and the two 32-bit timers (time-dependent) can initiate an interrupt. The output optocouplers are connected to a 37-pin Sub-D female on a board mounted slot bracket. Optocoupler inputs are connected to a 40-pin onboard box header. As an option a special plug-in cable set (female connector, flat ribbon cable and 37-pin female connector with bracket) is available, to relocate the connection to a slot of your PC case.

The pin assignment as of the optocoupler inputs and outputs is identical to ISA bus card OPTOIO-16, PCI bus card OPTOIO-PCI16 and PCIe bus card OPTOIO-PCIe16. Therefore a switch to PCIe16ultra is easy to implement.

Furthermore, the card provides a jumper block for card identification in order to distinguish several identical cards in your system.

# 2. Installation of the OPTOIO-PCIe16ULTRA

#### 2.1 Installation of the card into your system

Before you insert the OPTOIO-PCIe16 unplug the power cord or make sure, there is no current to/in the computer. Inserting the interface card in a running system may cause damaging or destroying not only the card OPTOIO-PCIe16<sub>ULTRA</sub>, but even other already inserted cards of your computer.

Select an empty PCIe slot of your computer for then inserting the card. Please refer to the computer's manual for support. Secure the circuit board by screwing the slot bracket to the casing of the computer to avoid a card's loosening by effects of the connecting cables.

# 3. Connectors

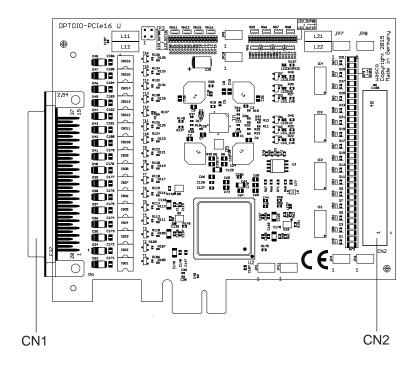

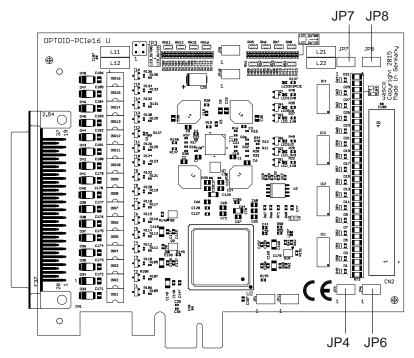

## 3.1 Position of the connector plugs on the board

CN1: Optocoupler Output OUT00...OUT15

CN2: Optocoupler Input IN00...IN15

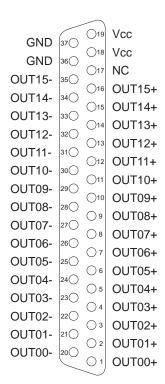

#### 3.2 Pin assignment of CN1

#### Vcc:

Connector for the card's internal voltage source (+ 5V) (a wiring bridge must be soldered to L11). **Never apply an external voltage across this pin.**

#### GND:

Ground connection (only when a wiring bridge is soldered to L12).

#### NC:

not connected

#### 3.3 Pin assignment of CN2

#### Vcc

Connector for internal voltage source (+ 5V) (a wiring bridge must be soldered to L21), **Never apply an external voltage across this pin.**

#### GND:

Ground connection (only when a wiring bridge is soldered to L22).

#### NC:

not connected

## 3.4 Pin assignment from CN2 to D-Sub37 (plug relocation kit)

#### VVcc:

Connector for internal voltage source (+ 5V) (a wiring bridge must be soldered to L21), **Never apply an external voltage across this pin.**

#### GND:

Ground connection (only when a wiring bridge is soldered to L22).

#### NC:

not connected

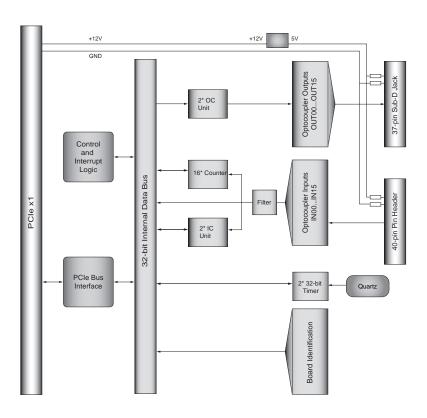

# 4. System Components

# 4.1 Block Diagram

#### 4.2 Access to the system components

You can access to the hardware components of the OPTOIO-PCIe16 by reading from or writing to Memory Mapped I/O addresses using library functions. The addresses relevant to the OPTOIO-PCIe16 arise depending on the BIOS assigned base address. Access to the OPTOIO-PCIe16 is exclusively in double-word access. For reasons of compatibility the wasco driver features only process or allow for the least significant byte. (You will find more information in the chapter Programming as well as in the sample programs on the supplied CD)

Fig. 4.1

# 5. 16 Optocoupler Isolated Digital Inputs

The OPTOIO-PCIe16 provides 16 input channels, each of which is optically isolated by optocouplers. The isolation voltage between GND and input is 500  $V_{DC}$ . The voltage within the input channels is limited to 50  $V_{DC}$ .

#### 5.1 Pin assignment of the input optocouplers

Fig. 5.1

## 5.2 Input voltage ranges

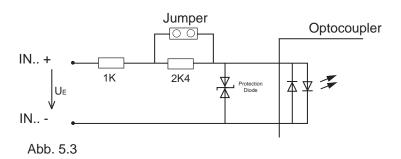

You can choose between two different input voltage ranges for each optocoupler input by setting jumpers on the blocks JP4, JP6, JP7 and JP8.

Fig. 5.2

For the data of the two input voltage ranges, please refer to the following table:

| Jumper | LOW  | HIGH   |

|--------|------|--------|

| closed | 01 V | 515 V  |

| open   | 02 V | 1430 V |

|      | JP4      |      | JP6       |      | JP7       |      | JP8       |

|------|----------|------|-----------|------|-----------|------|-----------|

| IN00 | 1 2      | IN05 | 1 2       | IN08 | 1 2       | IN13 | 1 2       |

| IN01 | 3 🔾 🔾 4  | IN06 | 3 🔾 🔾 4   | IN09 | 3 🔾 🔾 4   | IN14 | 3 🔾 🔾 4   |

| IN02 | 5 🔾 🔾 6  | IN07 | 5 () () 6 | IN10 | 5 () () 6 | IN15 | 5 () () 6 |

| IN03 | 7 🔾 🔾 8  | NC   | 7 () () 8 | IN11 | 7 🔾 🔾 8   | NC   | 7 🔾 🔾 8   |

| IN04 | 9 🔾 🔾 10 | NC   | 9 🔾 🔾 10  | IN12 | 9 🔾 🔾 10  | NC   | 9 🔾 🔾 10  |

By placing a jumper over Pin1 and Pin2 of the jumper block JP4 the input voltage range of IN00 changes from 0..2V (Low) and 14..30V (High) to 0..1V (Low) and 5..15V (High). The remaining input voltage ranges keep unaffected.

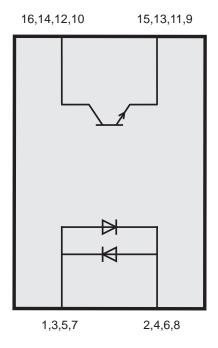

# 5.3 Input wiring

## 5.4 Input current

$$I_E \approx \frac{U_E - 1,1V}{3400\Omega}$$

(Jumper open)

$$I_E \approx \frac{U_E - 1,1V}{1000\Omega}$$

(Jumper closed)

#### 5.5 Access to the inputs

In order to determine the state of the optocoupler inputs, the register OPTOIN has to be read out. Every bit of the 32-bit value stands for one input as shown in the register table.

#### Application example:

As an example every third optocoupler input of the input plug shall be set to HIGH and all the rest to LOW. When the register OPTOIN is read, the card returns the value 0x4444(hex)/17476(dec)/0b0100010001000 100(bin). Out of this value you can filter the states of every single input by an AND-link operation.

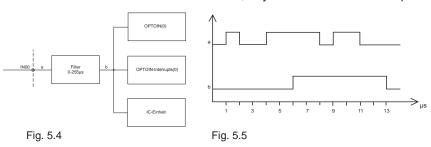

#### 5.6 Optocoupler inputs with digital filters

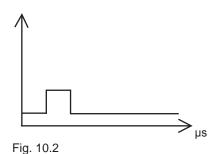

Each of the optocoupler inputs of the board WASCO-PCle8117 has its own configurable digital filter to filter spurious pulses and transients of the input signal.

For that the filter checks whether or not a signal is applied long enough, as shown in fig. 5.5. If this is not the case, a too short pulse for example will be ignored. In register OPTOINFILx you can adjust the minimum time of how long the signal has to be applied to be considered. You can adjust a filter width of 0 - 65535 $\mu$ s in steps of 1 $\mu$ s.

In state of default the filter is deactivated, say the filter duration is 0 µs.

Using the filters please note, that the optocoupler inputs on one hand have response times much longer than 1µs and on the other hand may vary in steepness of rising and falling curves. This is not considered at the filter configuration, as the optocouplers may show varying component tolerances. The user has to allow for this by himself. Not considering these switching times may lead to a filtering out of signals at the optocoupler input, even though theoretically they are applied long enough.

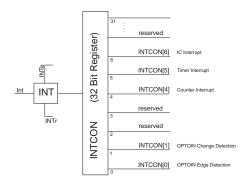

#### 5.7 Interrupt functions of the optocoupler inputs

To detect changes to the optocoupler inputs without periodically querying the input state via PC, the OPTOIO-PCIe16 offers several interrupt options. On one hand the card is aible to trigger an interrupt on one of the inputs on a rising edge. On the other hand the card can signal to the PC a general change of the input states by an interrupt.

For further information please see the chapter Interrupt Controller.

#### 5.7.1 Edge detection

In order to detect rising edges at the optocoupler inputs, each single input provides an edge detection with connectable interrupt function. For this purpose, a 32-bit interrupt register (OPTOINIF) is provided which makes available one bit per input channel for edge detection. As soon as the card detects a rising edge, the respective bit is set in register OPTOINIF. If at least one of the enabled bits is set, this will be passed over a line to the interrupt controller.

The interrupt function is enabled by writing the 32bit register OPTOINFe. Each single bit represents one input. As shown in the table port addresses (chapter 11.1) the respective bit indicates activation of the interrupt function with a 1 and deactivation with a 0. So, if the bit is 0, the corresponding bit in the register OPTOINIF will be set on a rising edge, but it will not be considered when the interrupt is triggered. All of the interrupt channels are deactivated in default state.

After the interrupt has been triggered, the source must be determined in the relevant interrupt service routine by reading the register OPTOINIF. Then the bit has to be cleared by setting the source channel bit in the register OPTOINFr. After the card has executed the reset command, the bit is reset automatically.

#### Application example:

You want an edge detection with interrupt triggering on channel IN01. The following example lists each step of how to perform the configuration and what needs to be done in the interrupt service routine to re-enable the interrupt.

Please note that in this example the interrupt configuration of the driver is not indicated. For the discription of this please refer to the driver.

Additional, more program examples are made available for download on our homepage.

#### Configuration:

- 1. Activation of the card's interrupt function (see chapter Interrupt Controller)

- 2. Enable the required interrupt

Before enabling an edge detection interrupt, please check whether or not the edge memory register OPTOINIF is reset completely. Otherwise, an interrupt might be triggered immediately after enabling the interrupt. If not all of the bits are reset in register OPTOINIF, value 0 is writtenxfffffff(hex) into the register OPTOINIFr.

See the table how to set bit 1 in register OPTOINIFe to activate an edge detection interrupt on channel IN01. This way, with the help of the PCIe write command, the value 0x00000002(hex) resp. 2(dec) is written to this register.

#### Interrupt Service Routine

- 1. To determine the interrupt source, the edge memory register OPTOINIF has to be read out (return value here 0x00000002(hex). If other sources are available, such as timer etc., please check in INTCON register whether or not the interrupt received from the PC is derived from the OPTOINIF register.

- 2. Once the source is identified, the source bit must be deleted. For this purpose, in our case write 0x00000002(hex) to the register OPTOINIFr.

#### Attention:

If in that time further interrupts were triggered (e.g. Timer), these must be deleted in their respective registers, too. Only after all of the activated interrupt registers have been reset to 0 again, another interrupt can be triggered.

# 5.7.2 Port Changes

If the optocoupler inputs often need to be queried to detect changes, another interrupt function can be used to relieve the PC. For this the WASCO-PCle8117 provides the possibility to trigger an interrupt in the event of a change at the inputs.

To enable this interrupt function on one hand the register OPTOINICe has to be set to 0x00000001. On the other hand, the user can determine via the 32-bit register OPTOINICCe, which one of the inputs should be considered for the detection. In the event of a change at the inputs, the corresponding bit is set in register OPTOINIC. To re-enable the interrupt after having been triggered, the corresponding bit in register OPTOINICr has to be set.

After the reset, the reset bit will be reset automatically.

#### 5.8 Port Addresses

| Offset  | Offset Register Name | Bit   | Bits                                                                                  |

|---------|----------------------|-------|---------------------------------------------------------------------------------------|

| Address |                      | Range | 31/15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 16/0 |

|         | O H                  | 31:16 | OPTOIN <31:16>                                                                        |

| OXOOOO  | 20.70                | 15:0  | OPTOIN <15:0>                                                                         |

| 0000    | OHIGH                | 31:16 | reserved (*)                                                                          |

| UXOOAO  | OF LOINTIEU          | 15:0  | reserved (*) OPTOINFIL0 <7:0>                                                         |

| 400     | OHO O                | 31:16 | reserved (*)                                                                          |

| UXUUA4  | OPI OINTIL           | 15:0  | reserved (*) OPTOINFIL1 <7:0>                                                         |

| 0       |                      | 31:16 | reserved (*)                                                                          |

| UXUUAS  | OP I OINFILZ         | 15:0  | reserved (*) OPTOINFIL2 <7:0>                                                         |

| 000     | C IIIIII 3           | 31:16 | reserved (*)                                                                          |

| טאטטאט  |                      | 15:0  | reserved (*) OPTOINFIL3 <7:0>                                                         |

|         | A HEIGH              | 31:16 | reserved (*)                                                                          |

| OXOODO  |                      | 15:0  | reserved (*) OPTOINFIL4 <7:0>                                                         |

| 7 0000  | FINIOTAC             | 31:16 | reserved (*)                                                                          |

| UXUUD4  | OF LOINFILS          | 15:0  | reserved (*) OPTOINFIL5 <7:0>                                                         |

|         | OBTOINEILE           | 31:16 | reserved (*)                                                                          |

| OXOOXO  |                      | 15:0  | reserved (*) OPTOINFIL6 <7:0>                                                         |

|         | 7 IIJINIEII 2        | 31:16 | reserved (*)                                                                          |

| OXOUBC  |                      | 15:0  | reserved (*) OPTOINFIL7 <7:0>                                                         |

|         | OBTOINEILS           | 31:16 | reserved (*)                                                                          |

| OXOOXO  | OFICINFILS           | 15:0  | reserved (*) OPTOINFIL8 <7:0>                                                         |

| 70000   | OBTOINE              | 31:16 | reserved (*)                                                                          |

| 00000   | OF LOUNT ILES        | 15:0  | reserved (*) OPTOINFIL9 <7:0>                                                         |

|         | OBTOINEII 10         | 31:16 | reserved (*)                                                                          |

| 020000  |                      | 15:0  | reserved (*) OPTOINFIL10 <7:0>                                                        |

|         |                      |       |                                                                                       |

| Offset  | Offset Register Name Bit | Bit   | Bits                                                                                  |

|---------|--------------------------|-------|---------------------------------------------------------------------------------------|

| Address | )                        | капде | 31/15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 16/0 |

|         | OCOCO                    | 31:16 | reserved (*)                                                                          |

| 220000  |                          | 15:0  | OPTOINFIL11 <15:0>                                                                    |

| 0000    | 0×00000 OPTOINEII 13     | 31:16 | reserved (*)                                                                          |

| 00000   |                          | 15:0  | OPTOINFIL12 <15:0>                                                                    |

| 70000   | 0.0004 OBTOINEII 43      | 31:16 | reserved (*)                                                                          |

| 0000    | OF LOUNTIELS             | 15:0  | OPTOINFIL13 <15:0>                                                                    |

| 00000   | O.OODS OBTOINE!! 44      | 31:16 | reserved (*)                                                                          |

| OXOODO  | OP I OIINFIL 14          | 15:0  | OPTOINFIL14 <15:0>                                                                    |

| 0000    | OVOODC OPTOINEII 1E      | 31:16 | reserved (*)                                                                          |

| חמסמס   | OF LOUNTIELS             | 15:0  | OPTOINFIL15 <15:0>                                                                    |

(\*) reserved area has to be assigned with 0

#### Register OPTOIN:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        |                   |                   |                   | ι                 | J                 |                   |                  |                  |  |

| 22,46        | U                 |                   |                   |                   |                   |                   |                  |                  |  |

| 23:16        |                   |                   |                   |                   | =                 |                   |                  |                  |  |

| 15:8         |                   |                   |                   | F                 | २                 |                   |                  |                  |  |

| 15.8         | OPTOIN <15:8>     |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          |                   |                   |                   | F                 | 2                 |                   |                  |                  |  |

| 7.0          |                   |                   |                   | OPTOIN            | l < 7:0>          |                   |                  |                  |  |

Bit 31 - 16 undefined

Bit 15 - 0 **OPTOIN <15:0>**

each bit corresponds to one optocoupler input (e.g. IN00 = OPTOIN<0>, IN13 = OPTOIN<13>) If a HIGH is applied to an input, the associated bit is 1, otherwise it is 0

## Register OPTOINFILx:

| _            |                    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|--------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 31:24        |                    |                   |                   | R/                | W                 |                   |                  |                  |  |  |  |

| 31.24        |                    |                   |                   |                   | -                 |                   |                  |                  |  |  |  |

| 23:16        |                    |                   |                   | R/                | W                 |                   |                  |                  |  |  |  |

| 23.10        |                    |                   |                   |                   | -                 |                   |                  |                  |  |  |  |

| 15:8         |                    |                   |                   | R/                | W                 |                   |                  |                  |  |  |  |

| 15.6         | OPTOINFILx < 15:8> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W                |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| /:0          |                    |                   |                   | OPTOINF           | ILx < 7:0>        |                   |                  |                  |  |  |  |

Bit 31 - 16 reserved (value 0 is written)

Bit 15 - 0 **OPTOINFILx <15:0>** (default = 0)

This value determines the filter duration of the filter x in µs

# 6. 16 Optocoupler Outputs

The OPTOIO-PCIe16 provides 16 output channels, each of which is optically isolated by optocouplers likewise. The isolation voltage between GND and output is 500 V.

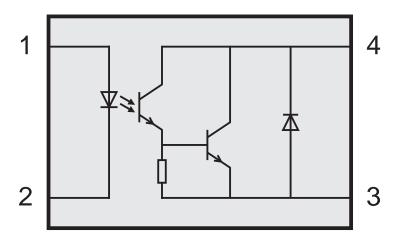

# 6.1 Pin assignment of the output optocouplers

# 6.2 Optocoupler data

Voltage CE: max. 50V Voltage EC: 0,1V Current CE: 150 mA

# 6.3 Output wiring

#### 6.4 Functions of the optocoupler outputs

#### 6.4.1 Basic function

The basic function of the optocoupler outputs allows the locking or enabling of the single outputs by writing to the 32-bit register OPTOOUT. In this register every single bit stands for one optocoupler output, as shown in table Port Addresses.

For example, if you want to connect every third output of the connector, you have to write the value 0 x4444(hex), 17476(dec) resp. 0b0100010001000100(bin) to the register OPTOOUT.

#### 6.4.2 Assigning optocouplers with other hardware components

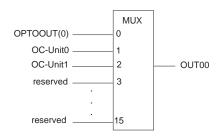

In addition to the basic function, which allows easy access to the optocoupler outputs, it is possible to assign different hardware components to the individual outputs, such as a PWM output (see Fig. 6.1). For this purpose, every optocoupler has a multiplexer with a 4-bit addressing (= up to 16 different sources). As a default source, the register OPTOOUT is specified as peripheral after a reset or when booting the PC. To change the source, the source address (see Fig. 6.2) has to be written to the register OPTOOUTMUXx

| Address       | Peripheral |

|---------------|------------|

| 0x0 (default) | OPTOOUT(x) |

| 0x1           | OC-Unit0   |

| 0x2           | OC-Unit1   |

| 0x3 - 0xF     | reserved   |

Fig. 6.1

Fig. 6.2

#### 6.5 Port Addresses

| Offset Address Oxogoo O | Bit Range 33:116 15:0 31:16 15:0 31:16 15:0 31:16 15:0 31:16 15:0 31:16 15:0 31:16 | Bits 31/15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 16/1  reserved (*)  OPTOOUT <15:0>  reserved (*)  OPTOOUTMUX0 [3:0] | 2 17/1 16/0  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31:16<br>15:0<br>31:16<br>15:0<br>31:16<br>15:0<br>15:0<br>16:0<br>31:16<br>16:0   | 25/9   24/8   23/7   22/6   21/5   20/4   1  reserved (*)  OPTOOUT <15:0>  reserved (*)  ed (*)                                                           | 17/1         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    | reserved (*) PTOOUT <15:0> reserved (*)                                                                                                                   |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    | PTOOUT <15:0> reserved (*)                                                                                                                                |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    | reserved (*)                                                                                                                                              |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    |                                                                                                                                                           |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    |                                                                                                                                                           | TMUX0 [3:0]  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u> </u>                                                                           | reserved (*)                                                                                                                                              |              |

| $\vdash$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                    | reserved (*) OPTOOUTMUX1 [3:0]                                                                                                                            | TMUX1 [3:0]  |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    | reserved (*)                                                                                                                                              |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    | reserved (*)   OPTOOUTMUX2 [3:0]                                                                                                                          | TMUX2 [3:0]  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | L                                                                                  | reserved (*)                                                                                                                                              |              |

| UXU3CC   OPTOOUTMUX3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15:0                                                                               | reserved (*) OPTOOUTMUX3 [3:0]                                                                                                                            | TMUX3 [3:0]  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31:16                                                                              | reserved (*)                                                                                                                                              |              |

| HQI UXUSDO   OPTOOUTIMUA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15:0                                                                               | reserved (*) OPTOOUTMUX4 [3:0]                                                                                                                            | TMUX4 [3:0]  |

| FOR PARTICIPATION AND AND AND AND AND AND AND AND AND AN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31:16                                                                              | reserved (*)                                                                                                                                              |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15:0                                                                               | reserved (*)   OPTOOUTMUX5 [3:0]                                                                                                                          | TMUX5 [3:0]  |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31:16                                                                              | reserved (*)                                                                                                                                              |              |

| UXUSDO   OPTODO IMUAO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15:0                                                                               | reserved (*) OPTOOUTMUX6 [3:0]                                                                                                                            | TMUX6 [3:0]  |

| ZVI MITI IOOTAO OASOVO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31:16                                                                              | reserved (*)                                                                                                                                              |              |

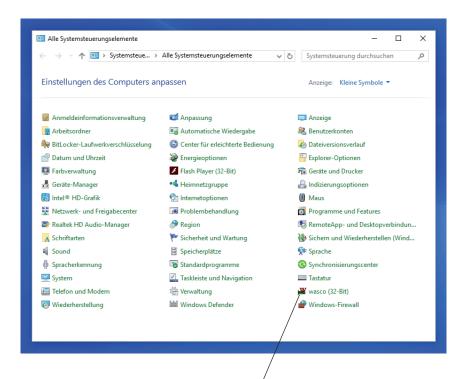

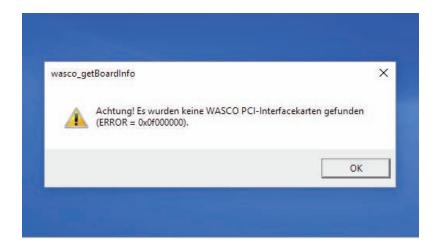

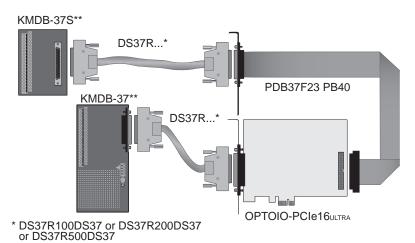

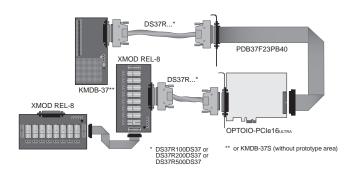

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15:0                                                                               | reserved (*)   OPTOOUTMUX7 [3:0]                                                                                                                          | TMUX7 [3:0]  |